1. CVD 공정의 개요

- CVD 방식의 종류

열에너지 이용 방식 : 대기압 CVD (APCVD)와 저기압 CVD (LPCVD)

플라즈마 에너지 이용 방식 : 플라즈마 CVD (PECVD)와 고밀도 플라즈마 CVD (HDPCVD)

원자를 표면에 흡착시키는 방식 : 원차층 CVD (ALCVD)

이러한 다양한 CVD의 종류는 품질, 속도, 성장 환경 등에 따라 가장 알맞은 방식이 선택됨

APCVD 저품질의 빠른 증착

LPCVD 고품질 높은 온도

PECVD 고온에서의 Thermal budget을 피하기 위해 낮은 온도

*Thermal budget이 높다는 것은 고온에서 오랜 시간 공정한다는 것으로 원치않은 diffusion이 일어날 수 있고 비용도 높아짐

- CVD 공정을 통한 유전체 박막의 역할

CVD 공정을 통한 유전체 박막은 정말 다양하게 활용됨

절연층, 이온주입 방지층, 도핑 공급용 박막 ,ARC(반사 방지 코팅), 하드 마스크, Capping 층, ESL(식각 방지층), 회로 보호층 등

- PMD, IMD, ILD 란?

Premetal Dielectric(PMD) : 금속 증착 이전에 사용되는 유전체

Intermetal Dielectric(IMD) : 여러 층의 금속 배선끼리의 합선을 막기 위해 절연 층이 필요하에 Metal 간의 절연 역할을 함

Interlayer Dielectric(ILD) : Si과 Metal을 절연해주는 역할을 함

* 추가적인 유전체 층이 증가할 때마다 새로운 이름이 아닌 ILD 용어 뒤에 숫자를 붙여 사용함

2. CVD 기본 개념

- CVD란?

CVD란 Chemical-Vapor Deposition의 약자로 가스 형태의 화학 전구체(Precursor)가 웨이퍼 표면에서 화학 반응을 일으켜 다른 원소로 변하면서 부산물(Byproduct)로써 고체형태의 박막이 형성되는 과정을 말함

*전구체(Precursor)란 기판에 고체 코팅을 증착하는 데 사용되는 휘발성 물질, 원하는 재료와 증착 조건에 따라 달라짐

CVD 공정 중 생성되는 기타 다른 종류의 부산물들은 가스 형태로 제거되어 기판에 남지 않음

Epitaxial Silicon, Polysilicon, Dielectric Thin Film, Metal Thin film 등 다양한 박막 증착에 적용됨

- CVD 증착 mechanism

1. 반응물(가스, 도판트)이 기판 영역으로 대류 혹은 확산되어 이동함

이때 열, 빛, 플라즈마 형태로 에너지를 공급해 기체 분자를 이온화하거나 높은 에너지 상태로 자발적으로 화학반응을 일으킬 수 있는 Radical 상태로 활성화 함

2. 기판 표면으로 운송된 Radical은 물리적 흡착 후 잠시 이동했다가 기판 표면의 원자와 화학 결합을 형성함

3. 박막 형성 mechanism을 통해 박막이 형성됨

4. 불안정하게 결합된 원자 혹은 박막 형성시 생성된 부산물들은 다시 탈착되어 진공펌프에 의해 외부로 배기됨

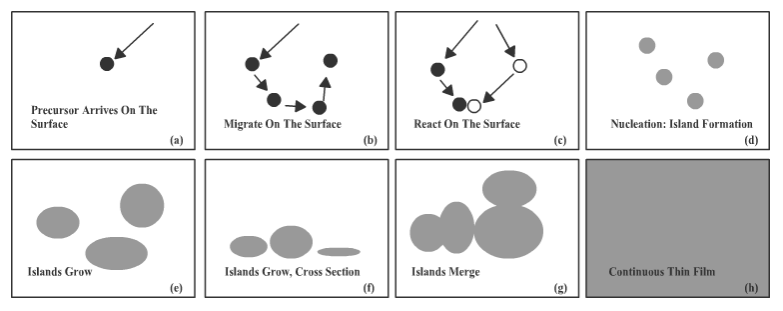

- 박막 형성 mechanism

1. 충분한 에너지를 가진 입자(원자, 분자, cluster)들이 기판 표면에 도달하여 물리적 흡착을 함.

2. 운동 에너지가 남은 원자들은 에너지를 줄이고자 표면 확산을 하게 되고, 결국 서로 뭉치게 됨

*만약 증착 가스가 여러 개라면 화학반응이 진행되게 됨

3. 1-2번이 반복되어 원자들이 서로 뭉쳐져 ‘cluster’ 형태를 띠게 됩니다.

4. 1-3번이 반복되어 cluster의 크기가 어느 정도 커졌으면 ‘핵’이 생성되게 됩니다.

5. 1-4번이 반복되어 ‘핵’이 부분 부분 생기게 되고, 이 핵들이 모여 ‘섬’ 이 형성됩니다.(Volmer-Weber 법칙)

6. 1-5번이 반복되어 섬 끼리 뭉치게 되어 박막이 형성되게 됩니다.

3. 다양한 CVD 공정

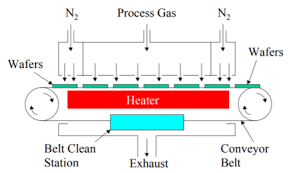

- Atmospheric Pressure(APCVD)

상압(~760 Torr)과 400~500도에서 증착이 진행됨

반응 챔버의 구조가 단순하며 상압에서 진행되기 때문에 진공펌프나 RF Generator가 필요하지 않음

*RF Generator는 반도체 및 디스플레이 제조 공정 중 Plasma를 사용하는 System에서 AC 교류 전 력을 RF 고주파 전력으로 변환해주는 장치

2개의 질소 버퍼 영역, 중앙의 프로세스 영역 총 세가지 영역으로 구성됨

공정 인자로는 온도, 프로세스 가스 유량 속도, 컨베이어 벨트 속도 등이 있음

저온 증착이 가능하고 증착 속도가 큼

상압에서 진행하다보니 step coverage가 우수하지 않으며 생산성이 낮음

가스 소모량이 크고 많은 particle 오염으로 인해 잦은 Cleaning 공정이 필요함

CVD 공정의 초기 형태로 주로 소자 내의 층간 절연막을 형성하는데 사용되었음

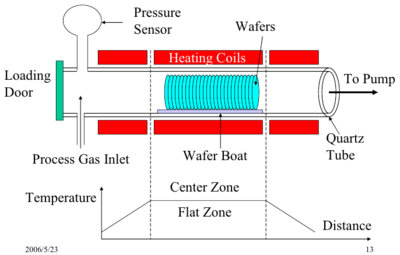

- Low-Pressure(LPCVD)

APCVD에 비해 0.1~10 Torr 저압에서 공정이 진행됨

저압에서 공정이 진행되기에 주입된 반응가스의 유속이 매우 빠름

* 이로인해 균일도는 좋아지나 확산계수 증가로 반응성이 감소하게 되고 기판 온도를 높임으로써 표면반응성을 높여 우수한 막질의 박막 형성이 어려움

* APCVD 기법에 비해 Throughput이 높음

우수한 step coverage를 가지며 pin-hole density 또한 낮음

저압에서 진행되어 particle 오염이 낮음

하지만 APCVD 대비 1/5 정도의 deposition rate을 가지고 900도 정도의 고온이기에 재려와 기판안정성을 확보해야함

열 산화 공정을 위한 퍼니스와 유사한 구조임

공정인자로는 웨이퍼 온도와 프로세스 가스 유량 속도 등이 있음

*이때 프로세스 가스 유량 속도는 상대적으로 덜 민감함

관련 자세한 내용은 https://sshmyb.tistory.com/80 참고

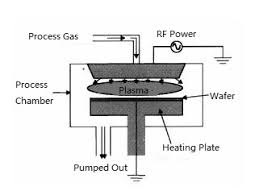

- Plasma Enhanced(PECVD)

저압(1~10 Torr)에서 플라즈마를 활용한 증착이 진행되는 기법

플라즈마로 인해 생성되는 자유 레디컬의 높은 화학적 반응성으로 인해 상대적으로 저온에서 빠른 속도로 박막 증착 가능

*플라즈마를 이용해 반응에 필요한 activation energy를 감소시켜 열역학적 한계를 극복가능함

금속 층 형성 이후에도 유전체 박막 성장이 가능

*APCVD는 금속 층 형성 후 사용이 불가함

관련 자세한 내용은 https://sshmyb.tistory.com/81 참고

4. Step Coverage(단차 피복)

- Step Coverage 개념

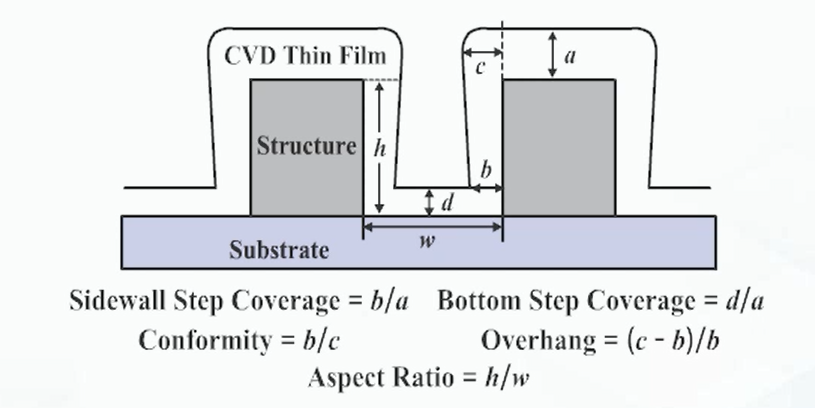

어떤 물질을 증착 했을때 위치에 따른 증착 두께의 비율을 의미함

즉 증착한 박막의 밑면과 벽면의 두께에 대한 비율을 조사할때 이용함

Sidewall Step Coverage 패턴구조 위에 증착되는 박막 두께 대비 측벽에 증착되는 두께 비율

Bottom Step Coverage 패턴구조 위에 증착되는 박막 두께 대비 패턴 사이 구멍 하부에 증착되는 박막 두께 비율

Conformality 패턴 상부 모서리 쪽에 증착되는 두께 대비 측벽에 증착되는 두께 비율

Overhang 패턴 상부 모서리 쪽에 증착되는 두께가 비율적으로 얼마나 큰지 나타내는 수치

- Step Coverage(단차 피복)에 영향을 주는 인자

# 반응물이 표면에 도달하는 각도(Arrival angle)

Arrival angle은 공정 압력과 관련이 있음

압력이 낮을시 mean free path가 증가하기 때문에 직진성이 커지지만 측면에 증착은 불리해짐

압력이 높으면 mean free path가 줄어들어 직진성이 감소해 단차 어깨부분에 증착되는 두께가 두꺼워짐

즉 적절한 압력 범위를 설정해 Arrival angle을 설정해야함

CVD 공정 압력이 감소하면 전구체의 mean free path가 증가함

MFP > Gap 깊이 h 일 경우 Gap 안에서 전구체가 이동시 기체 분자에 의한 충돌이 없고 이로인해 패턴의 코너에서부터 Gap 안쪽으로 전구체 이동이 용이해져 도달 각도가 감소함

도달 각도 감소 = Overhang 감소 = 단차 피복 증가를 의미함

도달 각도가 크면 상대적으로 더 많은 양의 전구체가 확산하여 도달함

도달 각도는 식각 공정에서 조절 가능하며 Tapered 컨택 홀 모양을 이용해 도달 각도를 크게함

*이후 W증착 공정으로 컨택 홀을 채우기 쉬움

# 전구체 표면 이동도(Precursor Surface Mobility)

표면이동도는 증착을 통해 생성된 박막이 표면에서 이동하는 정도를 나타낸 것

표면 이동도를 높이는 방법으로는 기판의 온도를 높이거나 반응성 기체 분자를 활용하는 방법이 있음

*기판의 온도를 높일시 SiO2의 품질이 떨어지는 단점이 존재함

*반응성 기체분자 TEOS(Tetra-Ethyl-Ortho-Silicate)를 이용함

표면 이동도가 낮아지면 단차피복이 감소함(= Overhang 현상 증가)

표면 이동도의 영향 인자는 전구체의 Chemistry, 웨이퍼 온도, 이온 포격 등이 있음

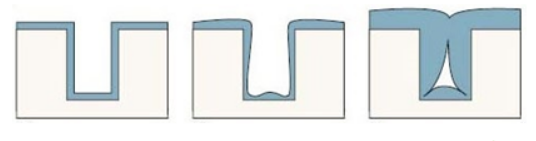

- Overhangs

단차 어깨쪽의 증착두께를 나타냄

도달 각도가 클수록, 표면 이동도가 낮을수록 두꺼운 Overhang이 형성됨

Overhang이 심할 경우 하부에 Void가 생성될 수 있음

*Void는 증착이 진행되는 과정에서 채워지지 못한 빈 공간을 말함

Void는 프로세스 가스가 포함되어 IC Chip으로 확산 가능해 불량을 유발함

일부의 경우 Void가 유전체의 유전율을 감소시켜 Low-K 역할을 하기도 함

증착 공정의 불량사례에 관한 내용은 https://sshmyb.tistory.com/303 참고

Low-k와 High-k에 관한 내용은 https://sshmyb.tistory.com/168#google_vignette 참고

5. Gap fill(Gap 채우기)

- Gap fill

컨택 홀 등의 Gap 형태의 패턴 구멍에 금속 등의 물질을 Void 없이 채우는 과정을 말함

반도체 위에는 수많은 요철이 있으며, 증착 과정에서 이 영역들을 꽉 채우기는 어려움

갭 필 특성이 좋지 않으면 내부에 Void가 생겨 추후 문제가 발생할 수 있음

*식각에는 원치 않는 부분이 깍여 나가는 등방성 문제가 존재, 증착에는 원하는 곳이 메꿔지지 않는 갭필 현상이 있음

*금속 CVD의 경우 전기전도도 감소, 가스 확산에 의한 소자 동작 불량 등의 문제 발생

*유전체 CVD의 경우 컨택 플러그 금속 층끼리의 단락 등의 문제 발생

- Gap fill 해결 방법

# Dep/Etch/Dep Gap 채우기, Ar+ 스퍼터링을 활용한 물리적 식각을 이용하며 증착 공정 사이에 Etchback 식각 공정을 삽입함, IMD공정에 널리 활용됨

# 높은 표면 이동도를 가지는 CVD 전구체를 활용해 균일한 증착 박막 형성하여 높은 단차 피복 수치와 낮은 Overhang 유도

6. Surface Adsorption(표면 흡착)

- Surface Adsorption(표면 흡착)이란

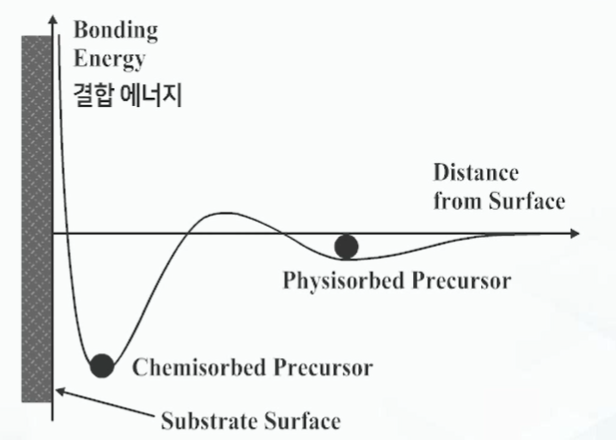

표면흡착이란 경계층을 넘어 확산해 온 전구체가 기판 표면에 흡착되는 현상을 말함

화학적 흡착 Chemisorption과 물리적 흡착 Physisorption 두가지 종류가 있음

- Chemisorption 화학적 흡착

화학적 흡착은 기판 표면을 구성하는 원소와 흡착된 전구체를 구성하는 원소 사이의 화학적 반응을 말함

2eV 이상의 결합에너지가 필요하며 비교적 강한 화학적 결합으로 인해 낮은 표면 이동도를 보유함

대부분의 유전체 CVD 공정온도는 450도 이상인데, 이때의 열 에너지(0.06eV) 이외에 플라즈마에 의한 이온 표격 에너지(10~20eV)를 이용해 화학적 흡착 결합을 깨뜨리고 표면 이동도를 확보함

- Physisorption 물리적 흡착

기판 표면을 구성하는 원소와 흡착된 전구체를 구성하는 원소 사이의 물리적 결합을 말함

Van Der Waals 결합 및 Dipole-dipole 결합으로 이루어짐

비교적 약한 물리 결합(<0.5eV)으로 상대적으로 높은 표면 이동도를 보유함

열 에너지와 플라즈마에 의한 이온 푝격 모두 활용가능하여 손쉽게 물리적으로 흡착된 결합을 깨뜨리고 높은 표면 이동도를 확보할 수 있음

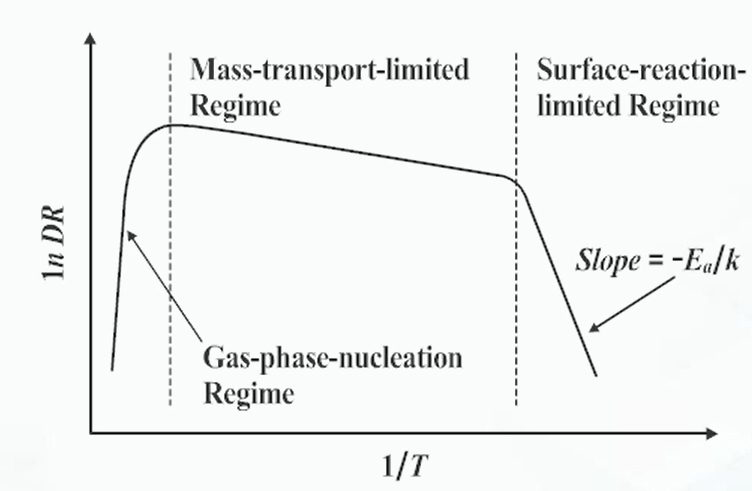

7. CVD의 Kinetics(CVD의 동역학)

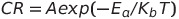

- Chemcial Reaction Rate (화학적 반응률)

CVD 과정에서 화학적 반응률 CR은 아레니우스 공식에 의해 결정됨

A : 상수

Ea : 활성화 에너지

Kb : 볼츠만 상수

T : 기판온도

활성화에너지 Ea가 낮아지면 CR이 높아져 화학반응이 일어나기 쉬워짐

전구체가 Ea 장벽을 극복하고 화학반응이 일어나기 위해서는 열, RF파워, UV조사 등의 외부적 에너지가 필요함

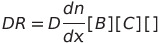

CVD공정의 경우 증착률 DR(Deposition Rate)과 연관있는 인자는 화학적 반응률(CR), 경계층을 통과하는 전구체의 확산률(D), 기판 표면에서의 전구체 흡착률(AR)등이 있음

온도에 따른 증착률(DR)은 세가지 영역으로 구분됨

저온 : Surface-Reaction-Limited Regime

화학적 반응률(CR)이 작은 상태로 DR은 온도에 민감함

기판 표면에 흡착되는 전구체가 쌓이는 상황

DR은 주로 CR에 의해 결정되며 CR은 온도에 의해 결정됨

일부 LPCVD 증착 공정(폴리실리콘, 비정질실리콘)에 활용됨

* [B],[C]..는 흡착된 전구체들의 농도

비교적 고온 : Mass-Transport-Limited Regime

DR은 온도에 민감하지 않음

CR이 충분히 높은 상황(=온도가 충분히 높은 상황)

기판 표면에 전구체가 흡착되자마자 화학 반응이 일어남

DR은 얼마나 빠르게 전구체가 확산되어 기판 표면에 흡착되는지에 따라 결정됨(확산률 D 및 농도 차이에 의존)

대부분의 CVD 공정에 사용하며 주입 가스의 유량 조절이 기판 온도 조절에 비해 용이하며 플라즈마에 의한 충분한 CR확보도 가능함

* dn/dx는 전구체 농도 차이

고온 : Undesirable Deposition Regime

가스의 핵형성에 따른 DR의 감소로 공기 중에서 파티클이 생성되어 잔여물이 발생함

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 12강 - 반도체 CMP 공정 (0) | 2024.06.25 |

|---|---|

| 【반도체 제조 개론】 10강 - 반도체 식각 공정 (1) | 2024.06.20 |

| 【반도체 제조 개론】 9강 - 반도체 이온주입 공정 (0) | 2024.06.19 |

| 【반도체 제조 개론】 8강 - 반도체 열처리 공정 (0) | 2024.05.27 |

| 【반도체 제조 개론】 7강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |