1. 열처리 공정의 개념

- 열처리 공정(Thermal Process)

반도체 IC Chip 제조 과정 중 웨이퍼가 처음 겪게 되는 공정으로 웨이퍼 표면 보호를 목적으로 실리콘 웨이퍼 상에 실리콘 산화막을 형성함

이온주입, 금속공정, 유전체 박막 증착 공정 이후에도 자주 쓰이는 공정으로 주로 고온의 퍼니스(Furnace)에서 진행됨

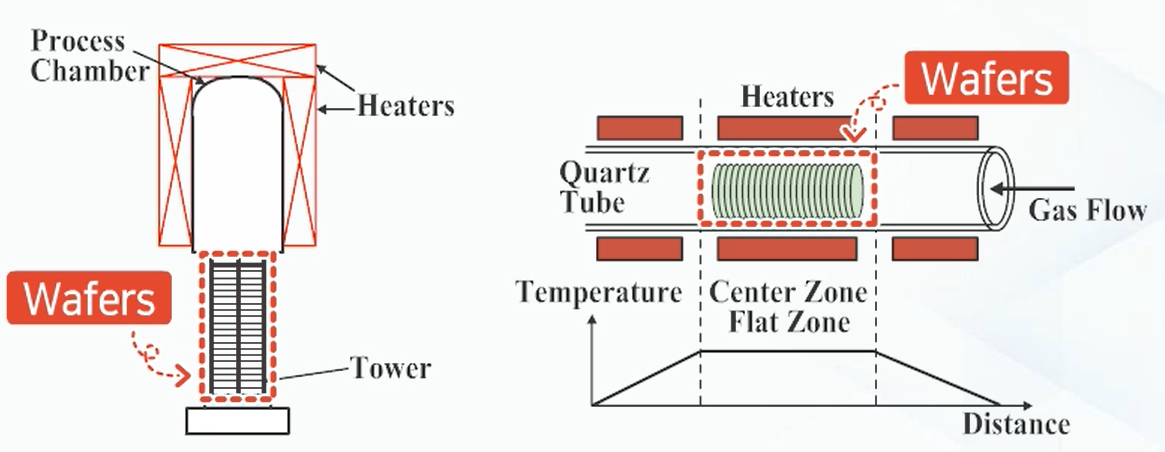

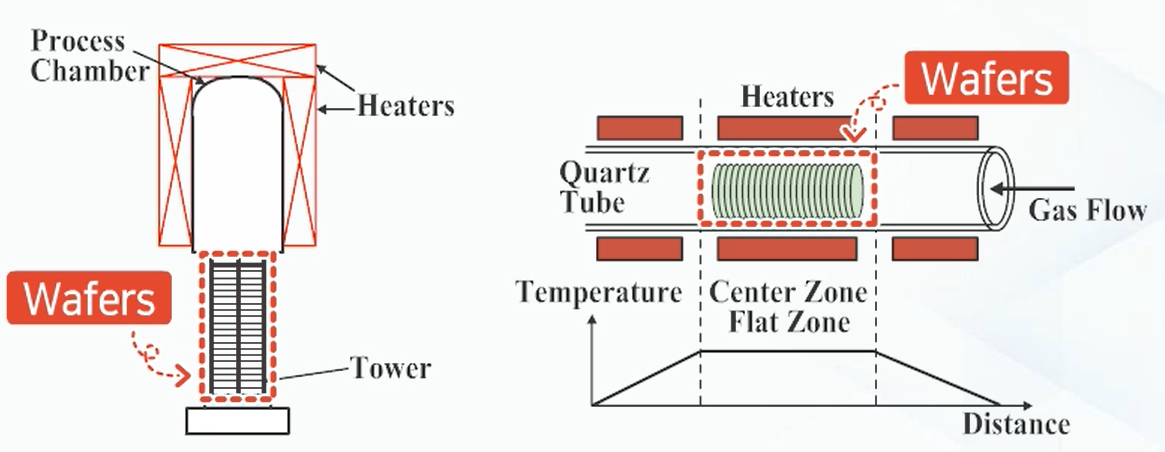

* Furnace는 일종의 화덕같은 장치로 반도체 열처리 과정에서 주로 사용되며 loading system, process tubes, gas delivery system, control system, exhaust system 등으로 이뤄짐

고온의 퍼니스는 균일도, 정확한 온도제어, 미립자 오염 저감, 빠른 생산성, 높은 재현성, 저비용들을 필요로함

이러한 공정은 대체로 700~1200도에 달하는 매우 높은 온도에서 진행됨

퍼니스의 종류로는 수평형(horizontal type)과 수직형(vertical type)가 있으며 수직형이 낮은 오염도, 큰 wafer 처리의 용이함, 균일성 때문에 더 자주 사용됨

2. 산화공정

- 산화공정

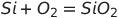

열처리 공정에 포함되며 실리콘 웨이퍼 상에 산소를 추가하여 고온에서 실리콘 산화막(SiO2)을 성장시키는 방법

* 산화막은 공정에서 발생하는 불순물로부터 실리콘 표면을 보호하는 막임

<산화막의 형성 방법>

열산화(Thermal Oxidation)

전기 화학적 산화(Elexctrochemical Oxidation)

화학적 기상 증착(Chemical Vapor Deposition, CVD)

플라즈마 화학 기상 증착(Plasma Enhanced Chemical Vapor Deposition, PECVD)

상온에서도 Si는 석영,모래로써 실리콘 산화막 형태로 존재하지만 우리가 원하는 것은 조금 더 두꺼운 산화막이므로 고온에서 화학반응을 함

약 1000도 이상의 고온에서 500nm 두께 산화막 성장 시, 수 시간이 소요될 정도로 매우 느린 공정임

100~200 장의 웨이퍼를 한번에 처리하는 Batch 공정도 있음

- 산화막의 용도

전기절연층 : MOSFET의 GATE 전극 절연층으로 사용

분리층 : 웨이퍼 위의 수천 수백개의 소자들 사이를 분리하기 위해 사용

표면 보호층 : 표면이 원치 않는 손상, 입자, 가스, 이온 등으로 부터 오염되는 것을 방지

공정 마스크로 사용 : 식각, 도핑 공정시, 표면을 막는 마스크 층으로 활용

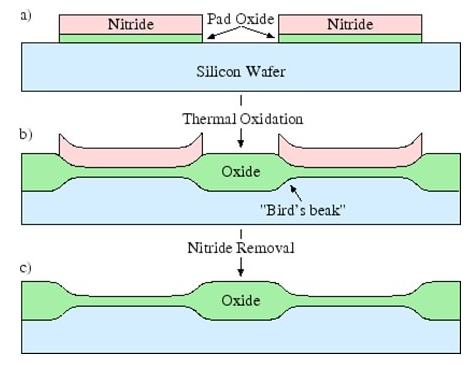

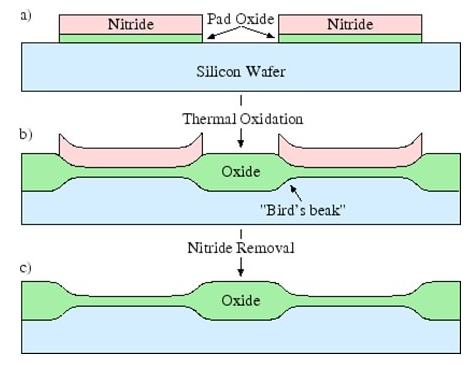

- LOCOS(Local Oxidation of Silicon) 공정

인접한 트랜지스터들을 분리해주는 전기적 절연층을 형성하는 과정임

이러한 과정을 Isolation이라 부름

* Isolation : 소자 사이에 절연 물질을 채워 소자를 전기적으로 분리하는 기술

실리콘 질화막(Nitride)은 산소 분자가 확산할 수 없는 층이라는 점을 이용함, 패드 산화막이 직접적으로 노출된 영역에 국한화여 산화 공정을 진행함

단점으로는 bird's beak라는 불량이 발생함, 이는 oxide가 소자 밑으로 침투해 소자가 위로 휘게 만드는 현상임

- STI(Shallow Trench Isolation)

반도체 기판에 트렌치를 형성하고, 트렌치 내부를 절연막으로 매립함으로써 소자분리막을 형성하는 기법

LOCOS 공정의 Bird's beak 현상을 개선하기 위해 사용되는 공정임

개별 소자 사이 영역의 Si 기판을 파내서 그 속에 oxide 물질을 채워 소자 사이를 전기적으로 분리하는 것임

패드 산화막(Pad Oxide)는 ~15nm두께로 실리콘 기판과 실리콘 질화막 사이의 인장력 차이에 대한 완충 역할을 함

배리어 산화막(Barrier Oxide)는 CVD 공정을 통한 USG 증착 시, 실리콘 기판의 오염을 방지함

* USG는 Undoped Silicate Glass로 도핑되지 않은 산화막을 의미함

LOCOS와 STI의 자세한 내용은 https://selectroing.tistory.com/entry/isolation-%EA%B3%B5%EC%A0%95-STI-Shallow-Trench-Isolation 참고

- 희생 산화막과 게이트 산화막

열 산화막은 주로 200mm 이하의 얇은 표면 보호막(패드 산화막, 배리어 or 라이너 산화막, 희생 산화막, 스크린 산화막) 및 게이트 산화막의 용도로 사용 중임

희생 산화막(Sacrificial Oxide) : 게이트 산화막이 성장되는 곳에 먼저 성장 되었다가 HF용액에 의해 식각됨, 실리콘 기판 표면의 결함과 손상을 제거하며 반도체 소자 특성과 직결되는 게이트 산화막 품질을 높이는 역할을 함

게이트 산화막 : 게이트 산화막의 두께는 게이트 전극의 반도체 채널에 대한 제어 능력과 연관이 있음, 두께가 얇을 수록 제어 능력이 커지게 됨

자세한 내용은 https://news.skhynix.co.kr/post/the-function-of-gate-oxide-and 참고

- 건식산화와 습식산화

여러 산화막의 형성 방법중 800~1200도의 고온에서 얇고 균일한 실리콘 산화막을 형성시키는 열산화 방법이 주로 사용됨

열산화 방법에는 건식산화(Dry Oxidation)와 습식산화(Wet Oxidation)가 있음

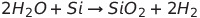

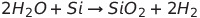

습식 산화(Wet Oxidation)

산소의 공급을 수분(H2O)으로 하여 실리콘 산화막을 성장하는 공정

산화막 성장 속도가 빠르고 동일한 온도와 시간에서 습식산화를 사용해 얻어진 산화막은 건식산화를 통해 얻어진 것보다 5~10배 정도 더 두꺼운 막을 형성할 수 있음

건식 산화에 비해 산화층의 밀도가 낮음

LOCOS 공정 등에 적용

건식 산화(Dry Oxidation)

산소의 공급을 산소 기체로 하여 실리콘 산화막을 성장하는 공정

매우 좋은 전기적 특성을 가진 산화물을 만들 수 있음

동일 온도, 같은 두께의 산하물을 형성하는데 습식산화보다 더 많은 시간이 필요함

박막 성장 속도는 느리지만 고품질의 산화막 형성 가능

패드 산화막, 게이트 산화막, STI라이너 산화막으로 사용됨

3. 확산 공정

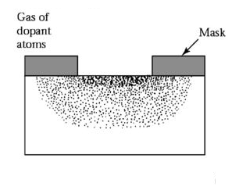

- 확산(Diffusion) 공정

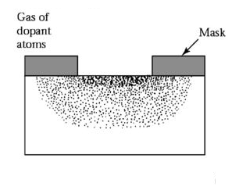

웨이퍼에 특정 불순물을 주입하여 반도체 소자 형성을 위한 특정 영역을 만드는 것

각 과정을 거친 회로 패턴의 특정 부분에 이온 형태의 불순물을 주입하여 전자 소자의 영역을 만들어 주고, Gas간 화학 반응을 통해 형성된 물질을 웨이퍼 표면에 증착함으로써 여러가지 막을 형성하는 공정

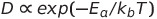

접합 깊이(Junction Depth) : 기판 불순물 농도와 확산에 의한 도핑 농도가 같아지는 지점으로 온도에 지수함수적으로 의존

Ea: The Activation Energy

kb : The Boltzmann Constant

T : Temperature

확산 공정은 접합 깊이와 도핑 농도를 정확하게 조절하기 어려움, 마스크 산화막 밑으로도 도핑 영역이 생성됨

현재로는 소스/드레인 이온주입 후 어닐링을 통한 확산(Drive in) 용도 정도로만 사용됨

자세한 내용은 https://blog.naver.com/esb2967/221553920650 참고

USJ(얕은 접합기술)의 공정 등 여러 연구 개발에 확산 공정은 여전히 사용됨

4. 어닐링 공정

- 어닐링(Annealing) 공정

웨이퍼의 물리/화학적 변화를 목적으로 고온 열처리 공정을 진행하는 것, 공정 전후로 추가적인 증착이나 식각이 없음

이온주입(Ion Implantation) 공정 시 계면에 데미지를 입은 웨이퍼에 상처가 아물도록 온도 변화를 주는 공정

과거 퍼니스를 이용한 고온 가열 방식에서 현재는 급속 열처리 방식인 RTA타입을 주로 사용함

* 퍼니스는 웨이퍼간 불균일성때문에 대체됨

- 합금 어닐링(Alloy Annealing)

고온에서 화학적 결합을 유도해 금속 합금이 만들어질 수 있도록 함

대표적으로는 코발트 실리콘 화합물이 있음(CoSi2), Self-aligned Silicide(Silicide,실리콘 화합물)로도 불림

자세한 내용은

https://news.skhynix.co.kr/post/self-alignment_silicide

https://news.skhynix.co.kr/post/silicide

참고

- 리플로우(Reflow), 납땜을 통한 안정성 확보

Glass 온도(Tg) 이상의 고온에서 규산염 유리가 말랑말랑해지는 현상을 이용하는 공정

Phosphosilicate Glass(PSG)의 경우 1100도에서 리플로우 공정이 가능함

표면이 부드러워지고 평평해지는 효과가 있으며 포토리소그래피 공정 시 Resolution 증가 및 메탈 공정 성공 확률 증가함

자세한 내용은 https://longtail3.thesecondstage.com/28 참고

5, 고온 CVD 공정

- 고온 CVD(Chemical Vapor Deposition) 공정

CVD공정은 화학적으로 막을 성장시키는 공정 기법임

칩 내의 트랜지스터가 ON/OFF 전기적 신호를 빠른 속도로 처리하려면 막 두께를 얇고 균일하게, 시간 변수에도 손상되지 않고 오래 버틸 수 있도록 만들어져야 함

실리콘 에피택시 증착, 폴리실리콘 증착, LPCVD 질화막 증착 등에 사용됨

주로 Low-pressure CVD(LPCVD)기법을 활용하는데, 이는 진공 시스템을 적용하여 불순물을 감소시키고 증착 속도 조절이 용이함

LPCVD 질화막은 반도체 공정에서 주로 확산 방지용 마스크로 활용함

자세한 내용은 https://news.skhynix.co.kr/post/chemical-film-growth 참고

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 10강 - 반도체 식각 공정 (1) | 2024.06.20 |

|---|---|

| 【반도체 제조 개론】 9강 - 반도체 이온주입 공정 (0) | 2024.06.19 |

| 【반도체 제조 개론】 7강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

| 【반도체 제조 개론】 6강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

| 【반도체 제조 개론】 5강 - 실리콘 웨이퍼의 필요성 (0) | 2024.05.24 |

1. 열처리 공정의 개념

- 열처리 공정(Thermal Process)

반도체 IC Chip 제조 과정 중 웨이퍼가 처음 겪게 되는 공정으로 웨이퍼 표면 보호를 목적으로 실리콘 웨이퍼 상에 실리콘 산화막을 형성함

이온주입, 금속공정, 유전체 박막 증착 공정 이후에도 자주 쓰이는 공정으로 주로 고온의 퍼니스(Furnace)에서 진행됨

* Furnace는 일종의 화덕같은 장치로 반도체 열처리 과정에서 주로 사용되며 loading system, process tubes, gas delivery system, control system, exhaust system 등으로 이뤄짐

고온의 퍼니스는 균일도, 정확한 온도제어, 미립자 오염 저감, 빠른 생산성, 높은 재현성, 저비용들을 필요로함

이러한 공정은 대체로 700~1200도에 달하는 매우 높은 온도에서 진행됨

퍼니스의 종류로는 수평형(horizontal type)과 수직형(vertical type)가 있으며 수직형이 낮은 오염도, 큰 wafer 처리의 용이함, 균일성 때문에 더 자주 사용됨

2. 산화공정

- 산화공정

열처리 공정에 포함되며 실리콘 웨이퍼 상에 산소를 추가하여 고온에서 실리콘 산화막(SiO2)을 성장시키는 방법

* 산화막은 공정에서 발생하는 불순물로부터 실리콘 표면을 보호하는 막임

<산화막의 형성 방법>

열산화(Thermal Oxidation)

전기 화학적 산화(Elexctrochemical Oxidation)

화학적 기상 증착(Chemical Vapor Deposition, CVD)

플라즈마 화학 기상 증착(Plasma Enhanced Chemical Vapor Deposition, PECVD)

상온에서도 Si는 석영,모래로써 실리콘 산화막 형태로 존재하지만 우리가 원하는 것은 조금 더 두꺼운 산화막이므로 고온에서 화학반응을 함

약 1000도 이상의 고온에서 500nm 두께 산화막 성장 시, 수 시간이 소요될 정도로 매우 느린 공정임

100~200 장의 웨이퍼를 한번에 처리하는 Batch 공정도 있음

- 산화막의 용도

전기절연층 : MOSFET의 GATE 전극 절연층으로 사용

분리층 : 웨이퍼 위의 수천 수백개의 소자들 사이를 분리하기 위해 사용

표면 보호층 : 표면이 원치 않는 손상, 입자, 가스, 이온 등으로 부터 오염되는 것을 방지

공정 마스크로 사용 : 식각, 도핑 공정시, 표면을 막는 마스크 층으로 활용

- LOCOS(Local Oxidation of Silicon) 공정

인접한 트랜지스터들을 분리해주는 전기적 절연층을 형성하는 과정임

이러한 과정을 Isolation이라 부름

* Isolation : 소자 사이에 절연 물질을 채워 소자를 전기적으로 분리하는 기술

실리콘 질화막(Nitride)은 산소 분자가 확산할 수 없는 층이라는 점을 이용함, 패드 산화막이 직접적으로 노출된 영역에 국한화여 산화 공정을 진행함

단점으로는 bird's beak라는 불량이 발생함, 이는 oxide가 소자 밑으로 침투해 소자가 위로 휘게 만드는 현상임

- STI(Shallow Trench Isolation)

반도체 기판에 트렌치를 형성하고, 트렌치 내부를 절연막으로 매립함으로써 소자분리막을 형성하는 기법

LOCOS 공정의 Bird's beak 현상을 개선하기 위해 사용되는 공정임

개별 소자 사이 영역의 Si 기판을 파내서 그 속에 oxide 물질을 채워 소자 사이를 전기적으로 분리하는 것임

패드 산화막(Pad Oxide)는 ~15nm두께로 실리콘 기판과 실리콘 질화막 사이의 인장력 차이에 대한 완충 역할을 함

배리어 산화막(Barrier Oxide)는 CVD 공정을 통한 USG 증착 시, 실리콘 기판의 오염을 방지함

* USG는 Undoped Silicate Glass로 도핑되지 않은 산화막을 의미함

LOCOS와 STI의 자세한 내용은 https://selectroing.tistory.com/entry/isolation-%EA%B3%B5%EC%A0%95-STI-Shallow-Trench-Isolation 참고

- 희생 산화막과 게이트 산화막

열 산화막은 주로 200mm 이하의 얇은 표면 보호막(패드 산화막, 배리어 or 라이너 산화막, 희생 산화막, 스크린 산화막) 및 게이트 산화막의 용도로 사용 중임

희생 산화막(Sacrificial Oxide) : 게이트 산화막이 성장되는 곳에 먼저 성장 되었다가 HF용액에 의해 식각됨, 실리콘 기판 표면의 결함과 손상을 제거하며 반도체 소자 특성과 직결되는 게이트 산화막 품질을 높이는 역할을 함

게이트 산화막 : 게이트 산화막의 두께는 게이트 전극의 반도체 채널에 대한 제어 능력과 연관이 있음, 두께가 얇을 수록 제어 능력이 커지게 됨

자세한 내용은 https://news.skhynix.co.kr/post/the-function-of-gate-oxide-and 참고

- 건식산화와 습식산화

여러 산화막의 형성 방법중 800~1200도의 고온에서 얇고 균일한 실리콘 산화막을 형성시키는 열산화 방법이 주로 사용됨

열산화 방법에는 건식산화(Dry Oxidation)와 습식산화(Wet Oxidation)가 있음

습식 산화(Wet Oxidation)

산소의 공급을 수분(H2O)으로 하여 실리콘 산화막을 성장하는 공정

산화막 성장 속도가 빠르고 동일한 온도와 시간에서 습식산화를 사용해 얻어진 산화막은 건식산화를 통해 얻어진 것보다 5~10배 정도 더 두꺼운 막을 형성할 수 있음

건식 산화에 비해 산화층의 밀도가 낮음

LOCOS 공정 등에 적용

건식 산화(Dry Oxidation)

산소의 공급을 산소 기체로 하여 실리콘 산화막을 성장하는 공정

매우 좋은 전기적 특성을 가진 산화물을 만들 수 있음

동일 온도, 같은 두께의 산하물을 형성하는데 습식산화보다 더 많은 시간이 필요함

박막 성장 속도는 느리지만 고품질의 산화막 형성 가능

패드 산화막, 게이트 산화막, STI라이너 산화막으로 사용됨

3. 확산 공정

- 확산(Diffusion) 공정

웨이퍼에 특정 불순물을 주입하여 반도체 소자 형성을 위한 특정 영역을 만드는 것

각 과정을 거친 회로 패턴의 특정 부분에 이온 형태의 불순물을 주입하여 전자 소자의 영역을 만들어 주고, Gas간 화학 반응을 통해 형성된 물질을 웨이퍼 표면에 증착함으로써 여러가지 막을 형성하는 공정

접합 깊이(Junction Depth) : 기판 불순물 농도와 확산에 의한 도핑 농도가 같아지는 지점으로 온도에 지수함수적으로 의존

Ea: The Activation Energy

kb : The Boltzmann Constant

T : Temperature

확산 공정은 접합 깊이와 도핑 농도를 정확하게 조절하기 어려움, 마스크 산화막 밑으로도 도핑 영역이 생성됨

현재로는 소스/드레인 이온주입 후 어닐링을 통한 확산(Drive in) 용도 정도로만 사용됨

자세한 내용은 https://blog.naver.com/esb2967/221553920650 참고

USJ(얕은 접합기술)의 공정 등 여러 연구 개발에 확산 공정은 여전히 사용됨

4. 어닐링 공정

- 어닐링(Annealing) 공정

웨이퍼의 물리/화학적 변화를 목적으로 고온 열처리 공정을 진행하는 것, 공정 전후로 추가적인 증착이나 식각이 없음

이온주입(Ion Implantation) 공정 시 계면에 데미지를 입은 웨이퍼에 상처가 아물도록 온도 변화를 주는 공정

과거 퍼니스를 이용한 고온 가열 방식에서 현재는 급속 열처리 방식인 RTA타입을 주로 사용함

* 퍼니스는 웨이퍼간 불균일성때문에 대체됨

- 합금 어닐링(Alloy Annealing)

고온에서 화학적 결합을 유도해 금속 합금이 만들어질 수 있도록 함

대표적으로는 코발트 실리콘 화합물이 있음(CoSi2), Self-aligned Silicide(Silicide,실리콘 화합물)로도 불림

자세한 내용은

https://news.skhynix.co.kr/post/self-alignment_silicide

https://news.skhynix.co.kr/post/silicide

참고

- 리플로우(Reflow), 납땜을 통한 안정성 확보

Glass 온도(Tg) 이상의 고온에서 규산염 유리가 말랑말랑해지는 현상을 이용하는 공정

Phosphosilicate Glass(PSG)의 경우 1100도에서 리플로우 공정이 가능함

표면이 부드러워지고 평평해지는 효과가 있으며 포토리소그래피 공정 시 Resolution 증가 및 메탈 공정 성공 확률 증가함

자세한 내용은 https://longtail3.thesecondstage.com/28 참고

5, 고온 CVD 공정

- 고온 CVD(Chemical Vapor Deposition) 공정

CVD공정은 화학적으로 막을 성장시키는 공정 기법임

칩 내의 트랜지스터가 ON/OFF 전기적 신호를 빠른 속도로 처리하려면 막 두께를 얇고 균일하게, 시간 변수에도 손상되지 않고 오래 버틸 수 있도록 만들어져야 함

실리콘 에피택시 증착, 폴리실리콘 증착, LPCVD 질화막 증착 등에 사용됨

주로 Low-pressure CVD(LPCVD)기법을 활용하는데, 이는 진공 시스템을 적용하여 불순물을 감소시키고 증착 속도 조절이 용이함

LPCVD 질화막은 반도체 공정에서 주로 확산 방지용 마스크로 활용함

자세한 내용은 https://news.skhynix.co.kr/post/chemical-film-growth 참고

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 10강 - 반도체 식각 공정 (1) | 2024.06.20 |

|---|---|

| 【반도체 제조 개론】 9강 - 반도체 이온주입 공정 (0) | 2024.06.19 |

| 【반도체 제조 개론】 7강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

| 【반도체 제조 개론】 6강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

| 【반도체 제조 개론】 5강 - 실리콘 웨이퍼의 필요성 (0) | 2024.05.24 |