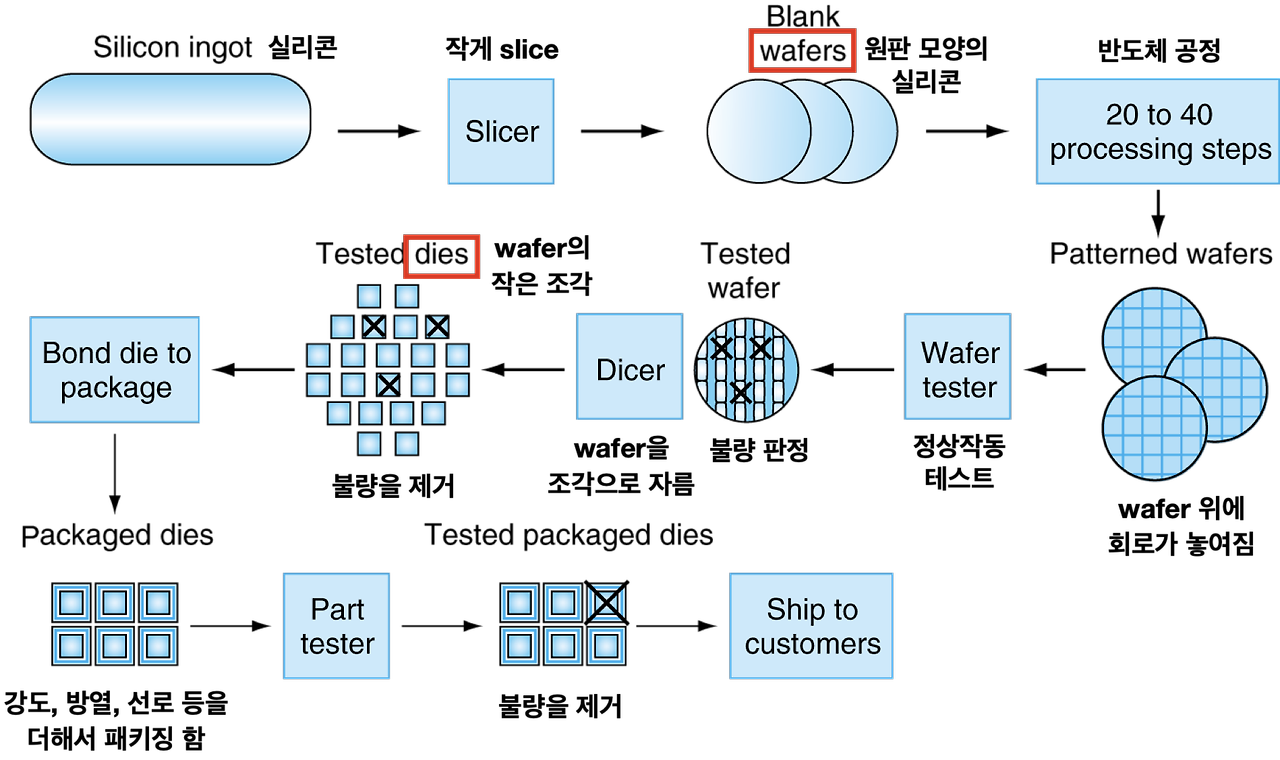

1. 반도체 IC Chip 제조 과정

- 반도체 IC(integrated Circuit) Chip 제조 과정

실리콘 잉곳 > 실리콘 웨이퍼 > 반도체 공정 및 소자 제작 > Chip(Die) > 패키징

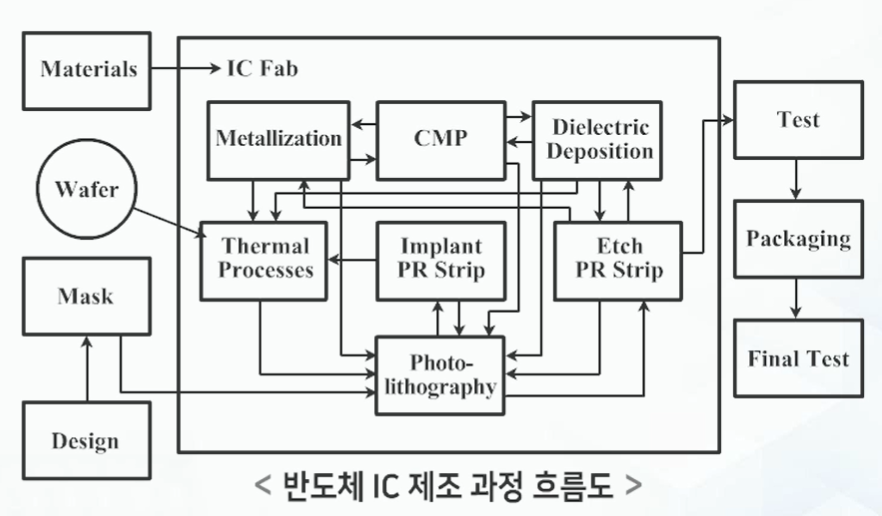

<반도체 IC 제조 과정 흐름>

IC 회로의 레이아웃 설계

실리콘 잉곳에서부터 웨이퍼를 제작함, 300mm 웨이퍼 기준

포토 마스크를 사용하여 회로의 레이아웃을 실리콘 웨이퍼 위에 전사하여 제작, 이때 포토리소그래피 기술 사용

* 포토리소그래피 : 빛을 사용하여 실리콘 웨이퍼와 같은 기판 위에 정밀하게 패턴화된 박막을 생성하는 미세 제조 기술

이때 고순도의 다양한 화학 물질들이 필요함

가스 형태 : 산소, 질소, 수소 등

액체 형태 : 증류수, 황산, 질산, 불화수소 등

고체 형태 : 인, 붕소, 알루미늄, 구리 등

웨이퍼 위에 다양한 반도체 공정이 진행됨

이때 공정 진행은 청정실(Cleanroom)이라는 대기 중 먼지 농도가 낮게 제어되는 시설에서 진행함

웨이퍼는 청정실 안에서도 특수 설계된 컨테이너에 보관함

반도체 공정이 완료된 웨이퍼는 검사, 패키징, 최종 검사 단계를 거침

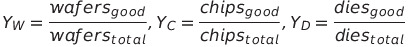

2. 반도체 공정에서의 수율

- 수율(Yield)

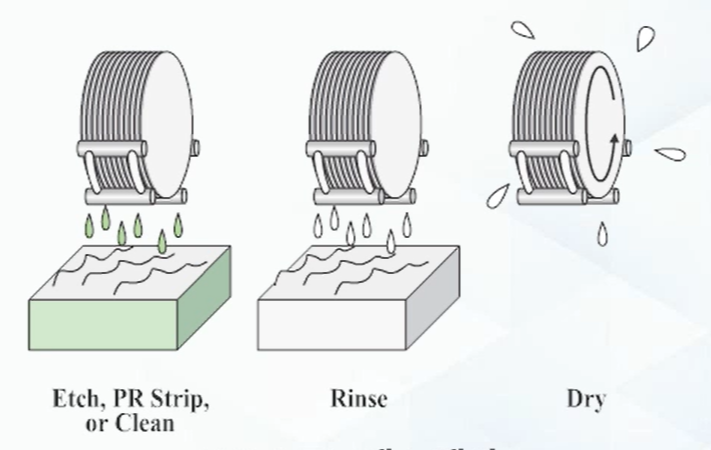

반도체에서 수율은 결함이 없는 합격품의 비율임

반도체는 미세회로로 구성되기 때문에 공정 중 어느 한 부분의 결함이나 문제점이 제품에 치명적인 영향을 미칠 수 있음

반도체 IC 제조 공정에서의 세 가지 수율 종류

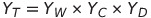

전체 반도체 수율은 각각의 곱임

킬러 결함 : 원하지 않는 결함 중에도 수율에 악영향을 끼치는 결함

킬러 결함에 의해 상품이 되지 못하는 칩의 면적이 클 수록 전체 수율은 저하됨

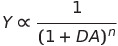

D : 킬러 결함 밀도, A : 칩 면적, n : 공정 단계 개수

오히려 상품용 반도체 소자나 회로를 직접 검사하는 것은 수율에 악영향을 줌

테스트 다이 및 구조를 활용해 반도체 공정 진행 중에 반도체 소자와 회로의 동작 성능을 체크함

만약 이를 활용해 전기적/물리적 불량이 발생하면, 해당 웨이퍼 이후의 공정은 진행하지 않음

3. 청절실의 개념

- 청정실의 기초

반도체는 아주 작은 미세먼지로 인해 오작동이 발생할 수 있어 반드시 엄격하게 통제된 청절실에서 생산해야 함

청정실 레벨은 Class로 구분함

* Class 10 : 지름이 0.5um 이상인 먼지가 세제곱 Feet 당 10개 미만

Class가 낮을 수록 더 높은 청정도를 가짐

공기중 먼지로 인해 포토마스크에 붙은 먼지에 의해 원치 않은 패턴이 생기거나, 이온 주입 공정 시 먼지에 의한 이온 주입 농도 차이가 발생할 수 있음

Killer 파티클 : 수율에 영향을 주는 형태의 먼지로 소자의 크기가 작으면 killer particle의 크기도 작음

상대적으로 큰 먼지는 바람에 의해 쉽게 탈착되기 때문임

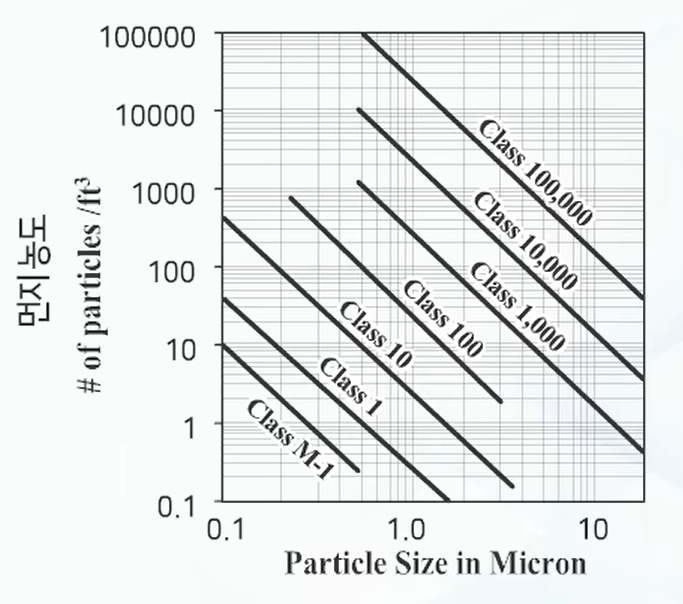

- 청정실 구조

바닥이 떠 있는 구조로, Grid 패널로 바닥이 구성됨

Hight-efficiency Particulate Air(HEPA) 필터는 공기중의 먼지를 필터링함

천장에서 바닥으로 수직적 공기 순환 시스템을 갖춤(Laminar Flow)

외부 공간 보다는 고압을 유지하여 밖에서 안으로의 먼지 유입을 차단

웨이퍼 자체는 FOUP라는 박스에 보관되어 운반되기 떄문에 청정실 공간 전체의 Class를 최소화할 필요는 없음

4. 반도체 공정의 4가지 기본 운용(Operations)

- Adding : Doping, Layer Growth, Deposition

도핑(Doping) : 반도체의 제조 과정에서 도핑은 의도적으로 진성 반도체에 불순물을 첨가함으로써 전기적 특성을 조절하는 것

에피택셜 성장(Layer Growth, Epitaxial growth) : 결정 기판 위에 방향성을 가진 결정막이 자라는 현상

증착(Deposition) : 웨이퍼 표면에 얇은 막을 씌워 전기적 특성을 갖도록 만드는 공정

에피택셜 성장은 실리콘위에 물질이 들러붙는 것이고 증착은 실리콘에 물질을 뿌리는 것임

- Removing : Etch, Clean, Polish

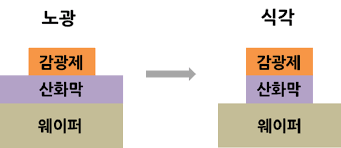

식각(Etch) : 금속이나 유리의 표면을 부식시켜 모양을 조각하는 것

Clean : 표면의 각종 오염물을 제거하는 것

연마(Polish) : 웨이퍼의 표면을 평탄하게 만드는 것

- Patterning : Photolithography

포토리소그래피(Photolithography) : 빛을 사용하여 실리콘 웨이퍼와 같은 기판 위에 정밀하게 패턴화된 박막을 생성하는 미세 제조 기술

- Heating : Annealing, Alloying, Reflow

어닐링(Annealing) 재결정화 온도 이상의 고온에서 오랫동안 금속을 노출시켜 금속을 더 부드럽게 만드는 작업, 이온주입 공정시 계면에 데미지를 입은 웨이퍼에 상처가 아물도록 온도 변화를 주는 공정임

합금(Alloy) : 반도체에 금속을 부착함

리플로우(Reflow) : 리플로우 공정은 솔더 범프에 형성된 산화막을 제거하기 위해서 반도체 소자와 기판 사이에 송진을 기반으로 만든 플럭스(Flux, 산화막의 환원을 촉진하기 위한 물질)를 도포한 후에 반도체와 기판을 정렬하고 가열하는 공정이다.

* 리플로우 관련 내용 https://www.etri.re.kr/webzine/20210611/sub03.html

5. 웨이퍼 프로세싱 구역(Areas or Bays)

웨이퍼 위에 반도체 소자를 제작/ 집적하는 공정이 이루어지는 곳

가장 낮은 Class(최고 청정도)가 유지되어야 함

Wet Bay, Diffusion Bay, Photo Bay, Etch Bay, Thin-film Bay, Chemical Mechanical Polishing Bay 등이 있음

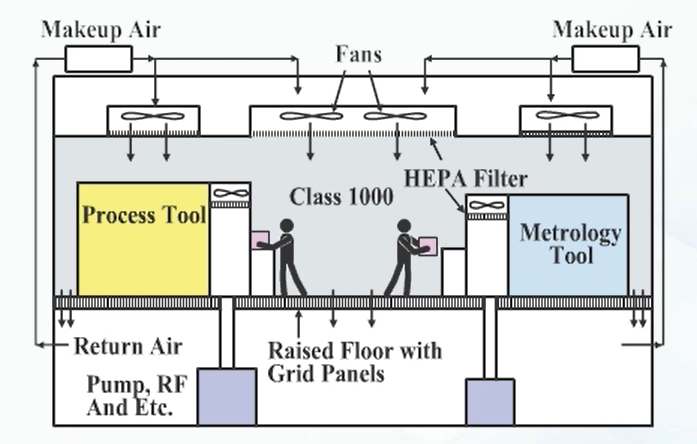

- Wet Bay

액체를 활용한 반도체 공정

Process, Rinse, Dry 3단계로 이뤄짐

Photoresis Stripping, Wet Etching, Wet Chemical Clean Proceses 등이 Wet Bay에서 이루어짐

부식성 화확물질 및 강한 산화제를 이용함 (HF,HCl,H2SO4,HNO3,H3PO4,H2O2 등)

- Diffusion Bay

열적 공정(Thermal Processes)이 이뤄짐

Adding Processes의 산화(Oxidation), 저압 화학 기상 증착(Low-pressure Chemical Vapor Deposition), 확산 도핑(Diffusion Doping)

Heating Processes의 이온주입 후 어닐링(Postimplantation Annealing), 도펀트 침투(Dopant Drive-in), 합금 어닐링(Alloy Annealing), 유전체 리플로우(Dielectric Reflow)가 Diffusion Bay에서 이뤄짐

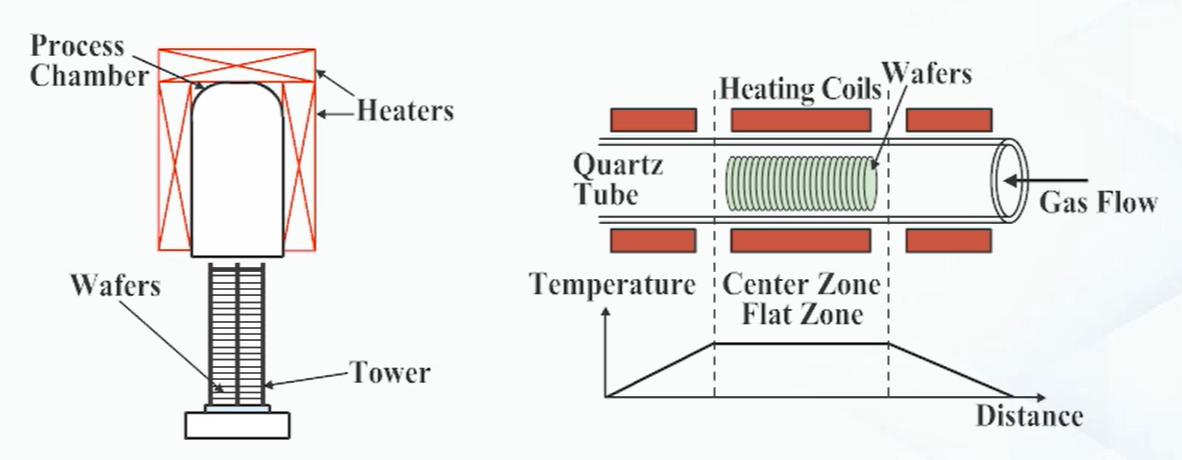

고온 퍼니스(Furnaces)와 다양한 가스가 필요함

* 퍼니스 : 열처리 장비로 외벽 coil로 퍼니스 전체를 가열하여 외벽과 내부 웨이퍼의 열적 평형을 요구함, 용광로라고 생각

- Photo Bay

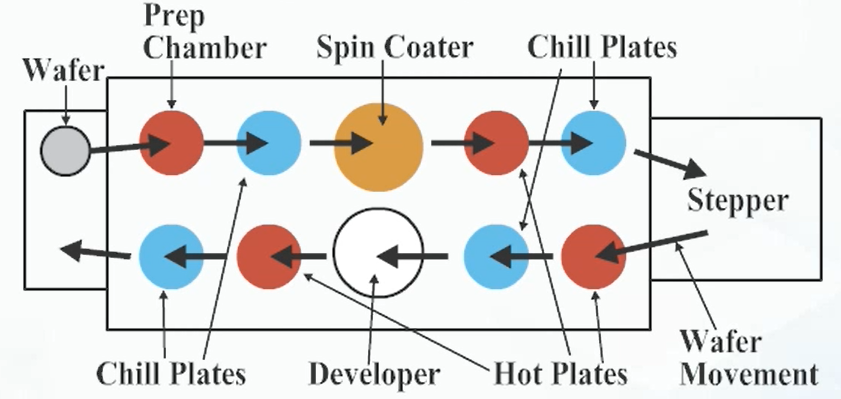

포토리소그래피 공정이 이뤄짐

포토레지스트 코팅(Photoresist Coating), 베이킹(Baking), 정렬 및 노광(Alignment and Exposure), 현상 과정(Development Processing Steps)이 이뤄짐

스테퍼(Stepper) : 노광공정 과정에서 웨이퍼를 빛에 직접 노출시키는 장비

- Etch Bay

포토리소그래피 공정에서 패턴된 포토레지스트를 기반으로, 포토마스크의 디자인 패턴을 웨이퍼에 영구적으로 전사시키는 과정

Removal Process : 웨이퍼 표면에서 물질들을 물리/화학적으로 깎아내는 과정이 진행됨

이때 습식 식각 공정의 최소 패턴 길이는 약 3um로써 매우 크기 때문에 CMOS 기술에서는 주로 건식 식각 공정이 사용됨

<4가지 종류의 Etch 프로세스>

유전체 식각 공정(Dielectric Process)

실리콘 식각 공정(Silicon Etch Process)

폴리 식각 공정(Poly Process)

금속 식각 공정(Metal Process)

- Implant Bay

포토리소그래피 공정에서 패턴된 포토레지스트를 화용하여, 웨이퍼 표면에 불순물을 이온 형태로 주입하여 도핑하는 과정

Ion Implantation + Rapid Thermal Annealing(RTA, 급속 어닐링 공정)이 진행됨

Adding Process가 이뤄짐, 불순물이 실리콘 웨이퍼에 주입되어 해당 부분의 전도도가 변화됨

고전압(~100kV), 고자기장, 독성 및 폭발성 가스를 사용함

- Thin-film Bay

유전체 또는 금속 박막을 증착하는 역할

유전체 박막용 Bay와 금속 박막용 Bay를 구분함

유전체 박막용 Bay : CVD공정

유전체 박막 증착에 사용함 (Plasma-enhaced CVD)

* CVD : Chemical-Vapor Deposition의 약자로, 기체 상태의 화합물들이 기판 표면 상으로 이동, 반응하여 박막이 형성되게 만들어주는 장비

금속 박막용 Bay : PVD, CVD, EPD 등의 공정

금속 증착은 고진공의 챔버 내에서 진행하여 습기 제거를 통한 금속 박막의 산화를 방지함

금속의 종류에 따라 개별적 챔버 및 장비를 사용함

- Chemical Mechanical Polishing Bay , 제거

기계적 그라인딩과 액체류를 활용한 화학 반응을 함께 사용하여 웨이퍼 표면에 있는 물질을 제거함

Removal Process임

CMP의 종료로는 Silicate Glass CMP, Tungsten CMP, Copper CMP 등이 있음

* Silicate는 실리콘과 산소를 포함하는 모든 화합물을 통칭함

Post-CMP Cleaning 공정이 꼭 필요함, CMP 공정 후 세척과정으로 웨이퍼 표면의 남은 조각을 제거하는 역할임

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 8강 - 반도체 열처리 공정 (0) | 2024.05.27 |

|---|---|

| 【반도체 제조 개론】 7강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

| 【반도체 제조 개론】 5강 - 실리콘 웨이퍼의 필요성 (0) | 2024.05.24 |

| 【반도체 제조 개론】 4강 - 차세대 반도체 단위 소자의 특징과 종류 (1) | 2024.05.20 |

| 【반도체 제조 개론】 3강 - 반도체 단위 소자의 동작 파라미터 (0) | 2024.05.18 |