1. CMOS 기술과 TFT 기술

- CMOS 기술과 TFT 기술의 비교

<CMOS기술>

컴퓨터 및 스마트폰에 들어가는 CPU, GPU, AP, Memory 등

MOSFET 형태를 제작하는 전반적인 분야 및 기술에 사용됨

TFT보다 기술 관련 산업이 큰 파이를 차지함

<TFT기술>

각종 디스플레이 패널에 적용

Thin Film Transistor의 약자

디스플레이 패널의 빛을 조절하는 핵심 반도체 소자임

집적도의 변화 : CMOS는 무어의 법칙을 좇는 형태지만 TFT는 향상 속도가 느림

기판,die 크기 변화 : CMOS는 기판 크기가 상대적으로 작아 크기 변화도 포화상태지만 TFT는 2.5년마다 2배씩 증가함

두 기술의 공통점 : 성능을 증가시켜 단가를 낮추는 방향으로 발전함

CMOS는 성능은 유지 및 개선하되 집적도를 증가시키려하며, TFT는 집적도보다는 큰 디스플레이 패널 면적에 고른 분포를 목적으로 함

| CMOS 기술 | TFT 기술 | |

| 레이어 성장 기술 | 주입 공정, 증착 공정, 에피택시 공정 | 증착 공정 |

| 공정 진행 온도 | 고온( > 600도) | 저온( < 600도) |

| 레이어의 품질 | 단결정 | 비정질 또는 다결정 |

| 채널의 캐리어 이동도 | 500 cm^2v-1s-1 | 0.5-200cm^2v-1s-1 |

| 기판 유형 | 반도체 기판 : 불투명 (웨이퍼) | 유리 또는 플라스틱을 포함한 모든 종류의 기판 : 투명 |

2. MOSFET 소자 스케일링 이슈

- MOSFET 소자 스케일링 이슈

단채널 효과의 발생

* 소자가 짧아짐에 따라 MOSFET의 채널 또한 짧아지는데, 이 때 발생하는 모든 현상

원래 Gate 전압에 의해서만 조절되어야 하는 채널이 소스/드레인의 전압에 의한 영향도 받게됨

MOSFET Turn Off 시에도 누설 전류의 발생으로 소비 전력이 증가함

더 자세한 내용은 참고 https://m.blog.naver.com/drcooper/221980672174

>> SCE(Short Channel Effect) 같은 부작용이 없는 새로운 형태의 MOSFET 반도체 소자 기술이 필요

대체 아키텍처 기술 : 기존 평면 구조외에 다른 구조의 MOSFET기술

신소재/신개념 기술 : 기존 실리콘 외에 새로운 반도체 소재 및 혁신적인 소재 조합 기술

- 대체 아키텍처 기술(다른 구조)

기존 구조로는 단채널 효과로 소스/드레인에 의해 채널이 조절됨

만약 채널 길이가 극단적으로 감소한다면 Vds(드레인 전압)에 의한 채널층 전하량 Q가 변화함

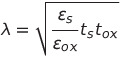

이때의 조건 : 채널 길이 L < 3배의 Characteristic 길이 λ, 즉 Channel length L <= 3λ 일때 단채널 효과 발생

즉 λ를 줄이면 단채널 효과가 발생하지 않음

ts: 반도체 두께, tox: 게이트 유전체 두께, εs: 반도체 유전 상수, εox: 게이트 절연체 유전 상수

이때 다른 파라미터들은 대부분 스케일링이 한계에 도달했지만, 반도체 층의 두께(ts)는 아직 스케일링 되지 않음

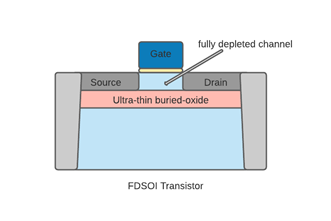

- FD-SOI (Fully Depleted Silicon on Insulator)

매우 얇은 채널용 실리콘을 가진 구조로 초박형 몸체 (Ultrathin Silicon Body, UTB) SOI라고도 불림

채널용 실리콘의 두께가 얇아서 전체가 공핍 전하층으로 만들어지는 Fully Depleted Device,FDD 를 만들 수 있음

* FDD는 게이트가 채널을 조절할 수 있는 능력이 큼

FDSOI의 구조

문턱전압 Vth 드랍을 보완하기 위한 Doping을 하지 않거나 아주 낮은 수준으로 농도를 낮출 수 있고 이로써 도핑으로 인한 캐리어와 불순물간의 산란 방지로 이동도도 개선 가능함

불순물 수 증가에 따른 Random Dopant Fluctuation에 의한 문턱 전압 변동 폭도 감소

* RDF : 트랜지스터의 이온주입 공정으로 불순물의 위치와 밀도가 무질서하게 변동하는 현상으로 Vth 변화를 유발하는 주요원인

FinFET이나 GAA에 비해 2차원 평판 구조여서 기술 사용이 용이함

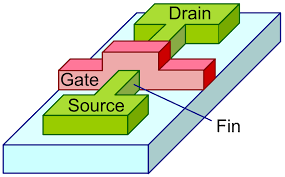

- FinFET

기존 평면(2D)의 한계를 극복하기 위한 입체(3D)구조, 구조가 물고기 지느러미(Fin)과 비슷해 FinFET으로 불림

게이트와 채널과의 접점이 클수록 효율이 좋아짐 >> Fin모양의 3D구조로 접점면적을 키워 반도체 성능 향상 및 누설 전류 감소

3. 신소재/신개념 기술 (새로운 반도체 소재 및 혁신적 소재 조합)

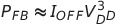

단채널 효과에 의한 누설전류의 증가로 소비전력이 증가하게 됨

전력소비 공식

드레인 전류값 상승으로 전력소마가 증가됨

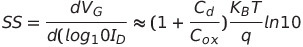

SubThreshold Swing(SS), 단위 [V/dec]

Threshold Voltage보다 작은 전압에도 불구하고 누설전압이 생겨 발생한 개념

SS는current 양이 10배 증가하는데 얼마의 전압이 필요한가?임

즉, gate voltage이 drain current 값을 10배 증가시키는데 필요한 전압을 의미

SS값이 작으면 소비전력 또한 감소하게 됨

하지만 기존 MOSFET의 온도에 따른 전자 주입 동작 원리에 따라 60mV/dec 미만으로 줄일 수 없음

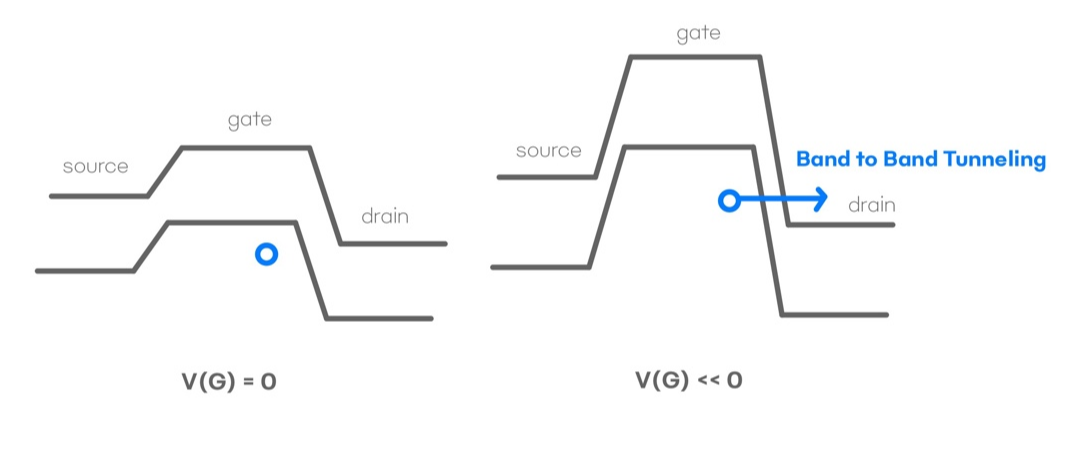

- T-FET (Tunneling FET)

전자의 파동성을 이용한 Tunneling으로 전류를 흘러 보내는 방식

* Band to Band Tunneling : gate에 음의 전압을 걸었을때 gate의 에너지 레벨이 올라감에 따라 얇아진 band gap을 전자가 통과해 drain쪽 conduction band로 넘어가는 현상

P+, i, n+ 구조의 접합으로 구성됨

Subthreshod 영역에서의 드레인전류를 획기적으로 감소시켜 SS값을 60mV/dec 미만으로 확보 가능

- NC-FET (Negative Capacitance FET)

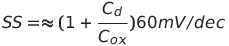

SS에서 Cox를 음수로 만들어 SS<60mV/dec으로 만드는 기술

음의 커패시턴스를 가질 수 있는 강유전체(Ferroelectric) 소재 활용

기존 MOS구조에서 강유전체를 삽입함, M-F-I-S 구조

기존 반도체 공정과 적합성이 뛰어남

2차원 층상 구조 소재로 그래핀, MoS2, 흑린 등이 사용됨

단원자층 두께로 두께 스케일링이 가능하여 반도체 두께(ts)를 극소화 가능- NC-FET (Negative Capacitance FET)

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 6강 - 반도체 공정 및 시설에 대한 이해 (0) | 2024.05.25 |

|---|---|

| 【반도체 제조 개론】 5강 - 실리콘 웨이퍼의 필요성 (0) | 2024.05.24 |

| 【반도체 제조 개론】 3강 - 반도체 단위 소자의 동작 파라미터 (0) | 2024.05.18 |

| 【반도체 제조 개론】 2강 - 반도체 단위 소자의 기본 구조 및 동작 원리 (0) | 2024.05.17 |

| 【반도체 제조 개론】 1강 - 반도체 분야와 개념 이해하기 (0) | 2024.05.16 |