1. PN 접합의 개념

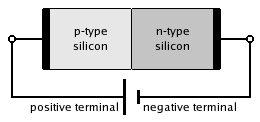

- PN 접합

P형 반도체와 N형 반도체의 접합

다이오드와 트랜지스터의 기본 구성요소임

P형 반도체와 N형 반도체가 접합하면 각각의 정공과 전자의 농도차에 의한 확산(Diffuision) 발생

이때 생기는 공핍층의 두께를 조절하여 전류가 한쪽 방향으로 흐를 수 있게 함

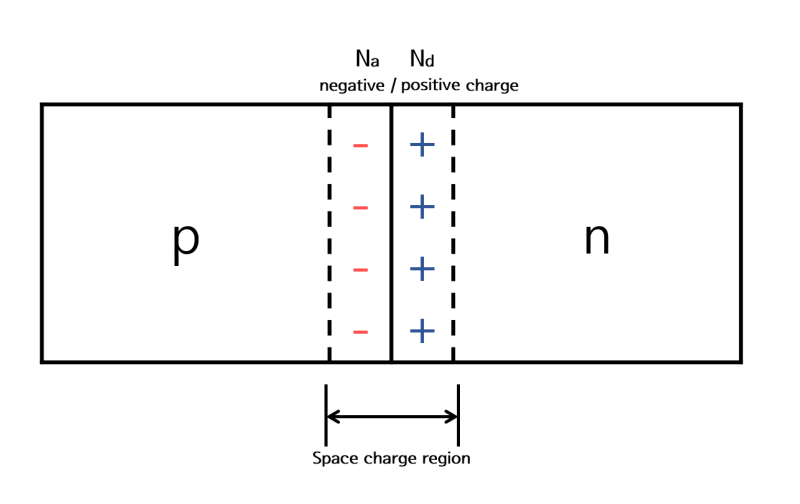

- PN 접합에서의 전하농도 변화 과정

P형 반도체와 N형반도체가 접합하면 전자와 정공이 재결합하며 공핍층이 형성됨

* 공핍층 : 접합면에서 일정부분 양 방향으로 캐리어가 없는 구간

P형의 높은 농도의 정공과 N형의 높은 농도의 전자가 각각 확산되는 것임

이 공핍층에는 공간전하(Space Charge)만 남게 됨

*공간 전하 : 순 양전하 및 음전하를 띤 두 영역을 공간 전하 영역이라 하며, 이동 전하가 결핍되어 있기 때문에 공핍 영역이라고도 함, PN접합에 아무런 전압이 공급되지 않으면 접합은 열평형 상태

P형의 acceptor 원자는 정공을 잃고 음이온이 되고, N형의 donor 원자는 전자를 잃고 양이온이 됨

확산 방향과 반대 방향의 전계가 걸리게 됨

공간전하에 의한 내부전위가 발생하여 전기장이 형성되고 이로인한 전기력으로 표동(Drift) 발생

* 표동 : 정공의 전자장에 대한 민감도, 전하의 농도와 이동도에 비례하며 전자장의 방향과 동일함, 유동전류는 공핍영역 안쪽에서 발생하며 확산과 유동의 균형으로 공핍영역이 더 이상 늘어나지 않음, 전자와 정공의 확산은 표동과 반대이기 때문

2. 다이오드의 동작 원리

- 다이오드

가장 기초적인 2단자형 반도체 소자로 PN접합으로 만들어짐

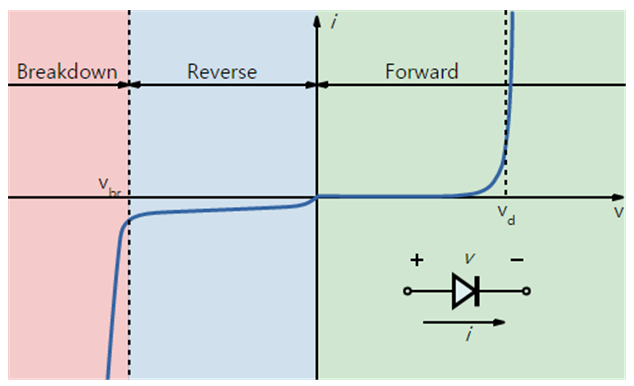

양방향이 아닌 단일 방향으로만 전류가 흐르며 순방향 바이어스가 인가되면 전류가 흐름

이때 순방향바이어스와 역방향바이어스를 이용해 다이오드에 흐르는 전류의 흐름을 제어함

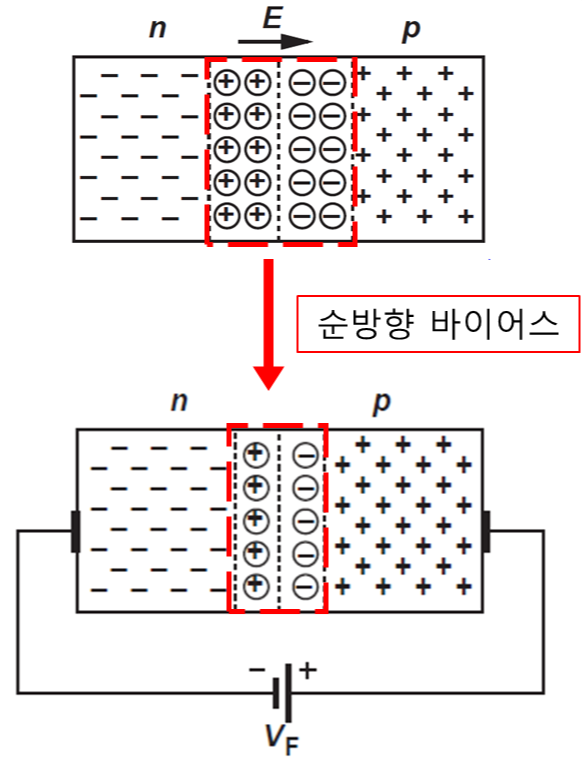

- 순방향바이어스

P영역에 양(+)의 전압, N영역에 음(-)의 전압을 인가함

P영역의 정공을 접합면으로 밀어내고 N영역의 자유전를 접합면으로 밀어냄

공핍층의 길이가 짧아져 전류가 흐름

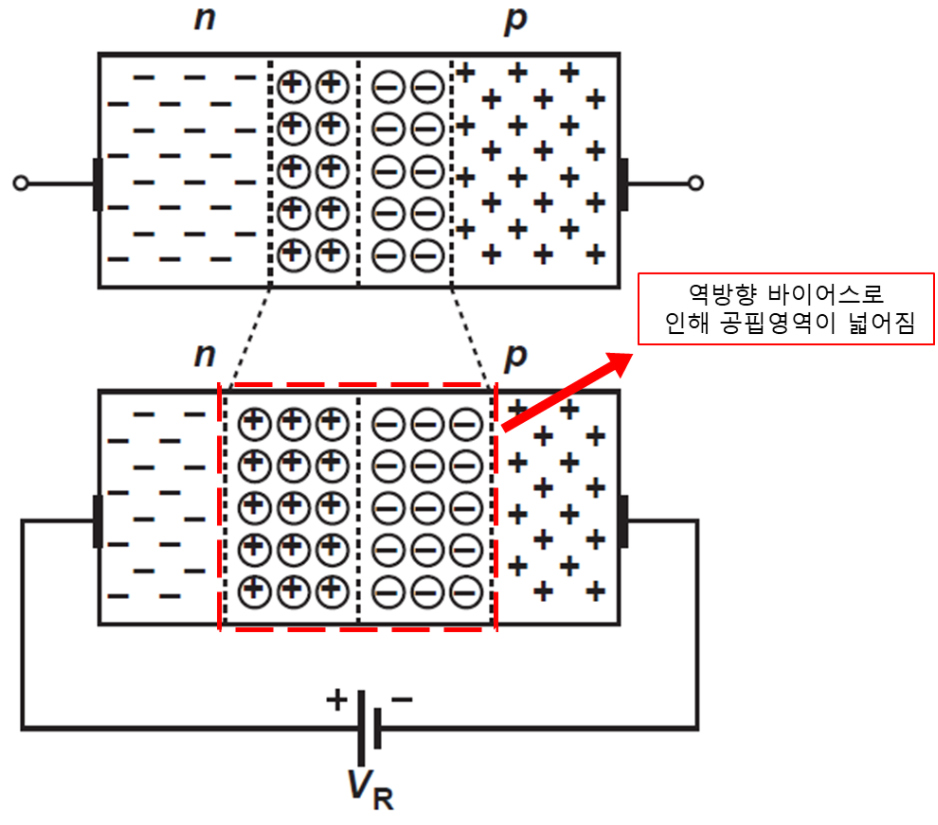

- 역방향바이어스

P영역에 음(-)의 전압, P영역에 양(+)의 전압을 인가함

접합면 근처의 정공은 P영역으로 끌려가고 접하면 근처의 자유전자는 N극으로 끌려감

공핍층의 길이가 길어져 전류가 흐르지 않음

* 공핍층의 길이가 커진다는 것은 전위장벽이 커진다는 것

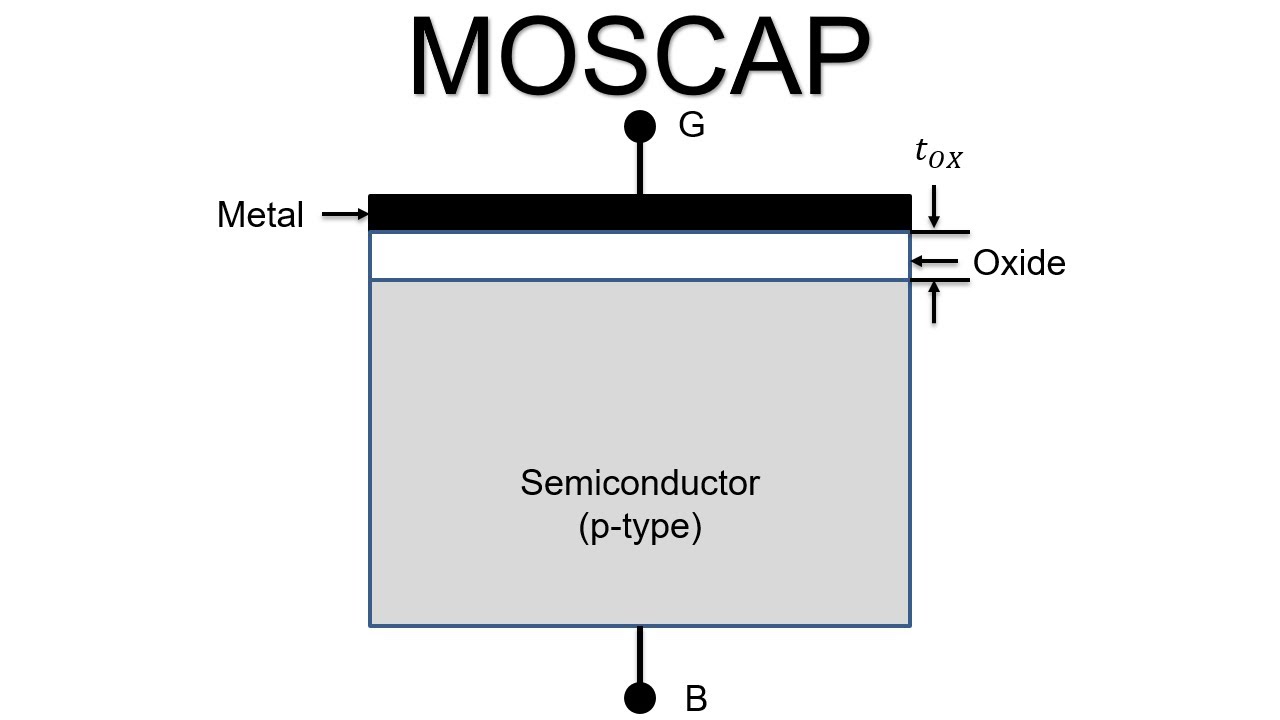

3. MOS 커패시터 구조

- MOS 커패시터 구조

MOSFET의 기본구조임

* MOS커패시터는 MOS(Metal-Oxide-Semiconductor) 구조로 2단자, MOSFET은 Gate, Source, Drain, Body 4단자 소자로 구성됨, MOS커패시터에 Source/Drain을 구성하면 MOSFET이 됨

*커패시터(capacitor)는 축적기 혹은 콘덴서로 전자회로에서 전기를 일시적으로 저장하는 장치임

MIS(Metal-insulator-semiconductor) 구조라고도 함

전계효과(Electric Field-effect)를 이용함

* 외부 전계(전기장)에 의해 반도체의 전기전도도가 변화하는 효과로 외부 전기장이 반도체 내부로 침투, 표면영역과 몸체영역이 나누어짐

관련 세부 내용은

https://sshmyb.tistory.com/18

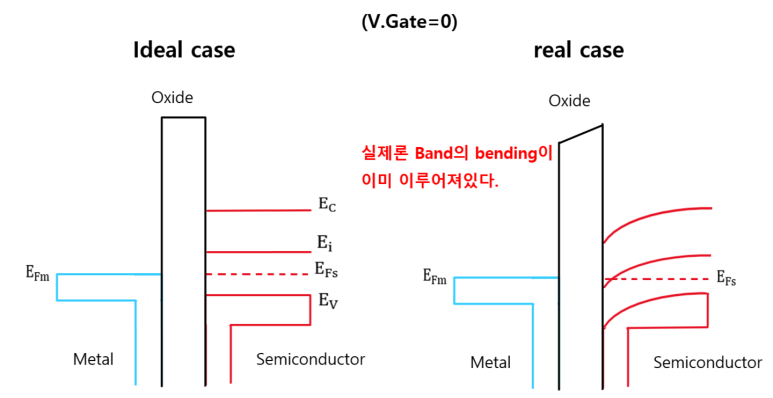

4. MOS 커패시터에서의 에너지 밴드

- MOS 커패시터 구조에서의 에너지 밴드

전계효과에 의해 에너지 밴드가 변화함

* flat band voltage : Real case에서 이미 band의 bending이 이루어져 있음, 이미 표면에 전자가 쌓인 것임, 다시 전압을 걸어 평평하게 Ideal case로 바꿔주어야함, 반도체의 페르미 레벨을 아래로 내려야 하기때문에 게이트에 음전압을 걸어야하는데 이것이 flat band voltage임

* 절연체의 커패시턴스 CI와 공핍층에 의해 생기는 커패시턴스 CS가 직렬연결된 구조

MOS구조 커패시턴스는 게이트 전압에 따라 변화하는 값을 측정함

* Si surface의 상태(Accumulation, Depletion, Inversion)

각 상태의 경계에 해당하는 값을 flatband voltage, threshold voltage라고 함

자세한 내용

https://m.blog.naver.com/balance-five/222145688715

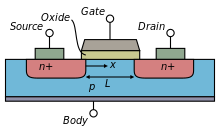

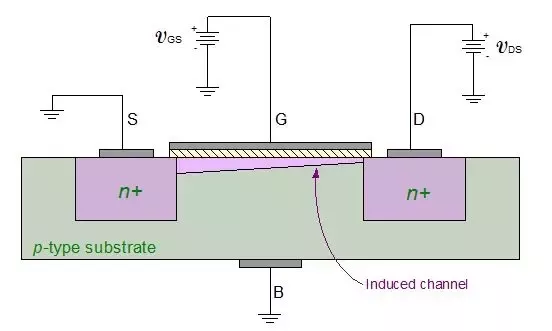

5. 전계효과를 사용한 트랜지스터

- 전계효과를 사용한 트랜지스터 제작

MOS 커패시터 구조 + 소스/드레인 도핑시 MOSFET이 됨

- MOSFET에서 채널(Channel)의 형성

N-MOSFET의 경우, 전자 채널을 형성하며, P-MOSFET의 경우 정공채널을 형성함

P-MOSFET의 경우, 게이트에 공급된 양의 전압 Vg는 정공들을 밀어내고 그 자리에 자유전자가 분포하게됨

이러한 자유전자들은 일종의 '채널'을 형성함하고 양 옆의 n타입 반도체가 이동할 수 있게됨

채널을 형성하기 위해서는 충분한 게이트 전압이 필요함 Vg>Vth>0V (Vth는 문턱전압 Threshold Voltage)

- MOSFET에서 전류의 흐름

드레인 전압(Vd)변화에 의한 드레인 전류(Id) : 출력 속성(Output Characteristic)

게이트 전압(Vg)변화에 의한 드레인 전류(Id) : 변환 속성(Transfer Characteristic)

Id-Vd특성은 저항처럼 비례하여 동작함

- MOSFET의 채널 형성

채널이 형성되기 위해서는 소스와 드레인의 x=0~L 모든 영역에서 게이트와 채널 간 전위차가 Vth 이상이어야 함

Vd가 충분히 크다면, 드레인 근처에서 채널 형성 안됨(채널의 끝부분이 막히는 pinch off 현상)

공핍층이 커져서 채널의 길이가 짧아졌다고 전류가 흐르지 않는 것은 아님, 해당 내부 전위에 의해 전자가 드레인 전극쪽으로 빨려들어 가기 때문

'공부 > 【반도체 공정】' 카테고리의 다른 글

| 【반도체 제조 개론】 5강 - 실리콘 웨이퍼의 필요성 (0) | 2024.05.24 |

|---|---|

| 【반도체 제조 개론】 4강 - 차세대 반도체 단위 소자의 특징과 종류 (0) | 2024.05.20 |

| 【반도체 제조 개론】 3강 - 반도체 단위 소자의 동작 파라미터 (0) | 2024.05.18 |

| 【반도체 제조 개론】 1강 - 반도체 분야와 개념 이해하기 (0) | 2024.05.16 |

| 【반도체 제조 개론】 0주차 - 목차 (0) | 2024.05.16 |