0. 이전 이야기

이전 포스팅에서는 Conventional Package의 Back-End 공정에 대하여 포스팅 했음

반도체 패키징에서 Back-End 공정은 몰딩, 언더필, 마킹, 솔더볼 어태치, 패키지 소팅, 테스트, 패키지 온 패키지 P o P 등의 단계로 구성됨

https://nate0707.tistory.com/170

【반도체 패키징】 4강-Conventional Package의 Back-End 공정

0. 이전 이야기이전 포스팅에서는 일반적인 Conventional package와 Filp-Chip package에 대하여 포스팅하였음Conventional package에는 백랩, 쏘잉, 다이 어태치 그리고 와이어 본딩 공정이 필요함플립칩 패키지

nate0707.tistory.com

반도체 패키징 기술이 발전하면서 TSV(Through-Silicon Via), WLP(Wafer-Level Packaging), PLP(Panel-Level Packaging) 등의 첨단 공정이 주목받고 있음. 특히, RDL(Redistribution Layer) 공정은 반도체 칩과 외부 기판 간의 전기적 연결을 최적화하는 핵심 과정임

1. RDL(Redistribution Layer) 공정과 Damascene 기법

- RDL(Redistribution Layer) 공정

RDL 공정에서는 기존 반도체 칩 위에 추가적인 금속 배선을 형성하여 신호 전송 경로를 재구성함

초기에는 알루미늄(Al)이 사용되었으나, 미세화가 진행되면서 저항 및 신뢰성 문제가 발생함

이를 해결하기 위해 구리(Cu)가 도입되었으나, 식각이 어려워지는 단점이 있음

- Damascene 기법

RDL 공정의 문제를 해결하기 위해 Damascene 공법이 사용됨

금속을 증착할 부분을 미리 파놓은 후 구리를 채우고, Chemical Mechanical Polishing(CMP) 공정을 통해 평탄화하는 방식임

Single Damascene: 금속 배선을 형성하는 공정

Dual Damascene: 배선과 함께 하부 배선과의 컨택(Via) 형성까지 동시에 진행하는 공정

*Cu 증착은 Electroplating 방식을 사용하며, PVD나 CVD 공정은 Void, Seam 등의 불량이 발생할 가능성이 높아 잘 사용되지 않음

*구리와 실리콘의 열팽창 계수 차이로 인해 스트레스가 발생할 수 있어, 도금 직후 어닐링 및 CMP를 통해 문제를 해결함

- Carrier Wafer

Carrier Wafer는 반도체 공정에서 기계적 지지를 제공하는 역할을 함

특히, 박막 웨이퍼(thin wafer) 가공 및 패키징 과정에서 필수적으로 사용됨

2. TSV(Through-Silicon Via) 공정

TSV는 반도체 칩 내부에 관통 비아(Via)를 형성하여 수직 전기적 연결을 가능하게 하는 기술임

고속, 고용량, 소형화, 저전력 등의 특성을 요구하는 메모리 반도체에서 필수적인 공정임

- 형성 시점에 따른 TSV 분류

Via First: 웨이퍼 가공 전에 TSV 형성

Via Middle: 웨이퍼 공정 중간에 TSV 형성

Via Last: 웨이퍼 후공정에서 TSV 형성

- Via Middle 공정의 순서

Thermal Compression (TC) 본딩: HBM(High Bandwidth Memory) 다단 적층

적층 이후 측면 혹은 전체 몰딩 진행

RDL을 통해 배선층 형성 후 Back-End 공정 수행

*PCB의 경우 패턴능력차이로 인해 기판과 칩을 합치기 어려운데, RDL은 자기 층에 맞는 형태로 회로패턴에 맞는 배선층을 만들 수 있음

3. WLCSP(Wafer-Level Chip Scale Package)와 PLP(Panel-Level Packaging)

- WLCSP(Wafer-Level Chip Scale Package)

WLCSP는 웨이퍼 레벨에서 패키징을 완료하는 기술로, 소형화 및 경량화가 가능함

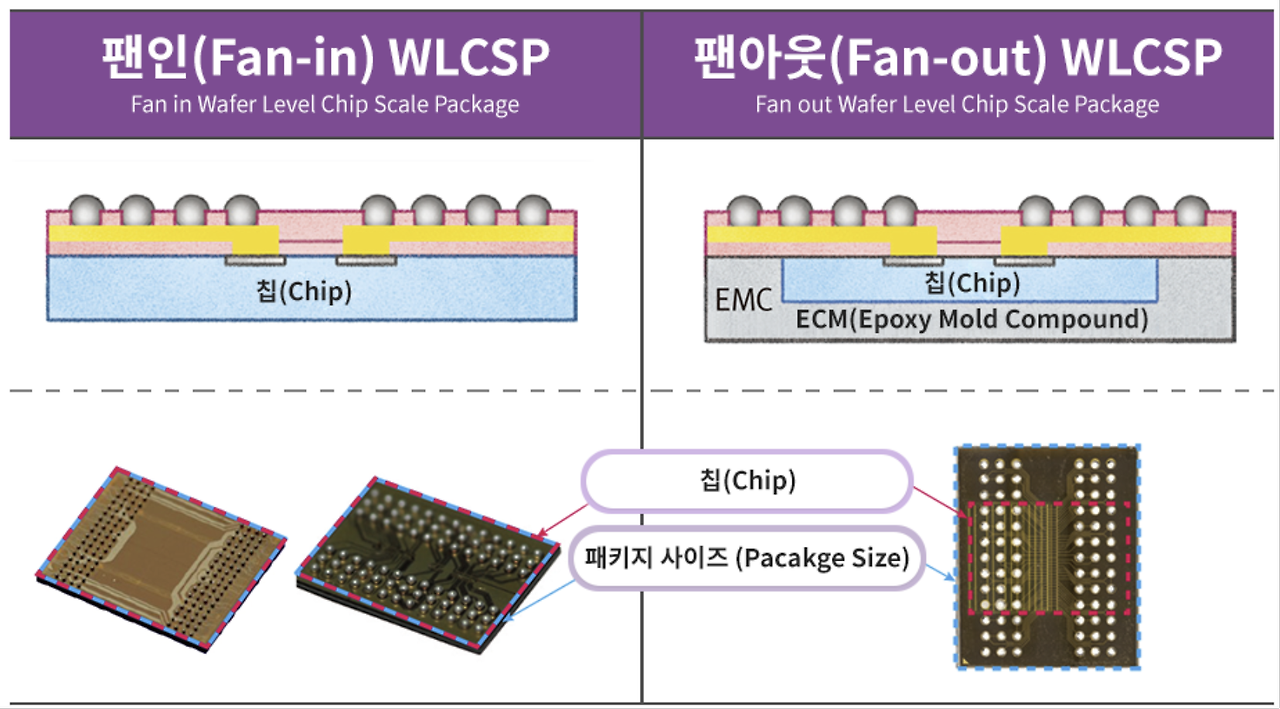

WLP는 Fan-In과 Fan-Out 방식으로 구분됨

이때 솔더범프가 칩사이즈 안에 있으면 Fan-In, 밖에도 있다면 Fan-Out으로 구분함

Fan-In WLP: 칩 크기 내에서 패키징이 이루어짐. 저전력 모바일 기기, RF 칩 등에 적합함

Fan-Out WLP: RDL을 활용하여 패드를 확장하는 방식. 고성능 AP, RF 칩, 자동차 반도체 등에 사용됨

Fan-In 방식은 웨이퍼 상태에서 진행하지만 Fan-Out 방식에서는 칩을 잘라서 캐리어 웨이퍼 위에 배치한 후 EMC로 몰딩함

그러나 초기에는 몰드 과정에서 EMC 흐름으로 인해 칩들이 변위되는 문제가 발생했음

이를 해결하기 위해 RDL First Fan-Out 방식이 등장하여 변위 문제를 해결함

*RDL을 먼저하여 고정하는 것임

- PLP(Panel-Level Packaging)

PLP는 개당 가격을 낮춰 가격 경쟁력을 확보할 수 있는 기술임

하지만 기존 장비가 원형 웨이퍼 기반으로 설계되어 있어 패널 방식 적용 시 공정 능력이 떨어지는 문제가 있음

4. Interposer 기술과 3D Stacked 패키징

- Interposer 기술

Interposer는 반도체 칩과 패키지 기판(PCB) 사이에서 전기적, 기계적 연결을 담당하는 중간층임

유기(Organic) 인터포저: 비용이 저렴하지만, 고온에서 Warpage(휨) 현상이 발생하고 표면이 거칠어 미세 회로 형성이 어려움

실리콘(Si) 및 유리(Glass) 인터포저: 표면 거칠기와 기계적 특성이 뛰어나지만, 비용이 높음. 최근에는 실리콘보다 저렴하면서도 성능이 우수한 유리 인터포저가 각광받고 있음

- Interposer의 역할

전기적 연결 최적화: 고속 신호 전송 및 전력 분배 효율 향상

기계적 지지: 칩과 기판 사이의 물리적 지지 역할 수행

패키징 유연성 제공: 다양한 반도체 칩을 통합하여 시스템 성능 향상 가능

열 관리 개선: 칩에서 발생하는 열을 분산하여 열적 안정성을 높임

- TSV 기반 3D Stacked 패키징

TSV 기반 3D Stacked 패키지는 다양한 방식으로 구현됨

Substrate 이용 TSV-3D Stacked 패키지: 마스터칩과 슬레이브칩을 PCB에 직접 부착하는 방식

KGSD(Known Good Stacked Die) 방식: Temporary Carrier에 부착 후 몰딩, 캐리어 제거 후 소잉을 거쳐 인터포저에 활용됨. 2.5D 패키징에서 CoWoS(Chip on Wafer on Substrate) 방식으로 구현됨

'공부 > 【반도체 패키징】' 카테고리의 다른 글

| 【반도체 패키징】 8강-반도체 패키징 불량 검사와 측정/분석 (0) | 2025.02.22 |

|---|---|

| 【반도체 패키징】 7강-반도체 패키지에서의 구조해석 (0) | 2025.02.22 |

| 【반도체 패키징】 4강-Conventional Package의 Back-End 공정 (0) | 2025.02.19 |

| 【반도체 패키징】 3강-컨벤셔널 패키지와 플립칩 패키지 (0) | 2025.02.19 |

| 【반도체 패키징】 2강-반도체 패키지와 개발 트렌드 (0) | 2025.02.18 |